MIPI DSI (Display Serial Interface) funktioniert als effizienter serieller Schnittstellenstandard, der von der MIPI Alliance entwickelt wurde. Es verbindet System-on-Chips (SoCs) mit Bildschirmen in Smartphones, Tablets und vielen eingebetteten Geräten. Setups haben in der Regel 1 bis 4 Datenspuren. Jede Spur verarbeitet bis zu 1,5 Gbps oder sogar mehr in neueren Versionen. Dies ergibt eine Gesamtbandbreite von bis zu 6 Gbps oder höher. Der Ansatz schneidet Pin-Nummern viel. Gleichzeitig sendet es Videodaten und Steuersignale gut.

Einführung in DSI

Moderne Bildschirme benötigen intelligente Wege, um Daten zu bewegen. Sie müssen sich problemlos mit hochauflösenden Bildern befassen. MIPI DSI diese Forderung erfüllt. Es bietet eine serielle Verbindung, die den Stromverbrauch und den Platzbedarf reduziert. Dies geschieht im Vergleich zu alten parallelen RGB-Schnittstellen. Bei Geräten mit 1440p Auflösung hält ein Frame beispielsweise über 5,6 Millionen Pixel. Bei 60 Hz-Aktualisierungsraten verarbeitet der Link etwa 340 Millionen Pixel pro Sekunde. MIPI DSI bewältigt dies mit schnellen seriellen Spuren. Diese verwenden eine niederspannungsdifferentielle Signalisierung, oft um 200 mV schwenkend. Dieser Schritt senkt elektromagnetische Störungen (EMI) und den Stromabzug.

Setups verfügen oft über eine dedizierte Uhrspur und 1 bis 4 Datenspuren. Bei D-PHY-basierten Systemen erreicht jede Datenspur bis zu 2,5 Gbps. Ein 4-Spuren-Setup erreicht dann fast 10 Gbps Gesamtbandbreite. Diese Menge funktioniert für 4K bei 60 Hz, sobald der Protokolloverhead berücksichtigt wird.

Die Schnittstelle läuft in zwei Hauptmodi, um effizient zu bleiben.

Hochgeschwindigkeitsmodus (HS)

Es schaltet sich für Frame-Updates während lebendiger Inhalte wie Video oder Scrolling an. Datenexplosionen passieren schnell. Sie sind oft in nur Millisekunden für eine Frame-Übertragung fertig.

Low-Power (LP) Modus

Dieser Modus tritt während stiller Inhalte oder ruhiger Zeiten ein. Die Datenraten fallen unter 10 Mbps. Die Leistung sinkt auf Mikrowatt. Das bedeutet über 99% Einsparungen im HS-Modus. Infolgedessen verbrauchen immer-auf-Displays sehr wenig Batterie. Sie können immer noch Dinge wie Zeit oder Benachrichtigungen anzeigen.

DSI bietet zwei Möglichkeiten, Daten zu senden.

Videomodus

Es streamt Pixel die ganze Zeit. Dies eignet sich für Anwendungen, die ständige Updates benötigen.

Befehlsmodus

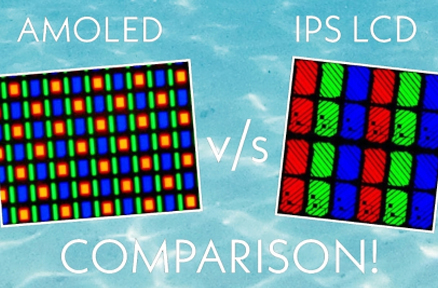

Dies ist bei AMOLED und vielen LCD-Panels üblich. Der SoC sendet komprimierte Bildpakete und zieht Befehle in einen Frame-Puffer auf dem Panel. Dann aktualisiert der Display-Treiber die Pixel selbst. Dadurch können die Schnittstelle und der Prozessor die meiste Zeit in niedrigen Leistungszuständen bleiben. Die Batterielebensdauer wird auf diese Weise viel länger.

Was sind D-PHY und M-PHY?

MIPI D-PHY und M-PHY bilden die Hauptphysikalische Schicht (PHY) Schnittstellen in der MIPI-Welt. Jedes entspricht bestimmten Leistungs- und Leistungsbedarf.

D-PHY ist die Standardwahl für mobile Displays und Kameras. Es stützt sich auf source-synchrone Taktung. Es verfügt über eine Uhrspur und mehrere Datenspuren. Der High-Speed-Modus unterstützt Geschwindigkeiten von bis zu 2,5 Gbps pro Spur (in Versionen v1.2). Der Low-Power-Modus verwaltet die Steuerung unter 10 Mbit/s. Ein normales 4-Spuren-D-PHY-Setup bietet fast 10 Gbps für 1080p bei 60 Hz. Es hält auch eine gute Energieeffizienz.

M-PHY zielt auf schwierigere Aufgaben ab. Dazu gehören Speicher, Modems und erweiterte Bildgebung. Es verwendet eingebettete Taktung mit 8b/10b-Codierung. Dadurch entfällt die Notwendigkeit einer separaten Uhrspur. Pinzählung fällt. Es ermöglicht auch dynamische Leistungszustände wie STALL, SLEEP und HIBERNATE. Diese führen zu geringeren Latenzen und größeren Einsparungen. Die neuesten Versionen (v5.0) erreichen mit skalierbaren Getrieben bis zu 11,6 Gbps pro Spur (z. B. Gear3 mit 5,8 Gbps, Gear4 mit 11,6 Gbps). M-PHY funktioniert gut für explosiven oder stabilen Verkehr in komplexen Setups.

Wichtige Unterschiede fallen hervor.

-

Taktung: D-PHY verfügt über eine spezielle Uhrspur. M-PHY baut die Uhr im Inneren.

-

Leistungszustände: D-PHY verwendet HS/LP-Modi. M-PHY bietet mehrere fortgeschrittene Zustände.

-

Geschwindigkeit: D-PHY erreicht bis zu ~2,5 Gbps/Spur. M-PHY steigt auf ~11,6 Gbps/Spur.

-

Anwendungen: D-PHY führt in Displays (DSI) und Kameras (CSI). M-PHY leuchtet in Speicher (UFS) und Interchip Links (UniPro).

D-PHY bleibt üblich für Displays. Es profitiert von langem Gebrauch, einfacherem Design und abgestimmter Leistung für Refresh-Muster. M-PHY sieht mehr Einsatz, wo hohe Bandbreite wichtig ist. Beispiele sind UHD-Video, AR/VR und Automobilsysteme.

Die Beziehung zwischen DSI und Physical Layer Interfaces

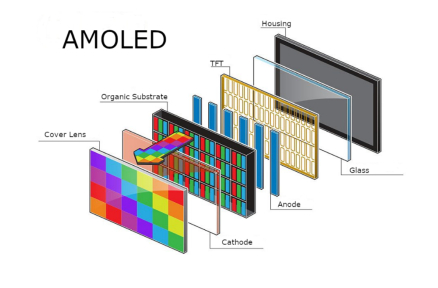

MIPI DSI legt das Protokoll fest. Es umfasst Datenorganisation, Paketstruktur, Timing und Befehle. Der PHY unterhalb verwaltet elektrische Signale über PCB-Spuren.

DSI erstellt Pakete, die Pixeldaten, Synchronisierungsinformationen und Anweisungen enthalten. Das PHY verwandelt diese in Differenzsignale. In D-PHY wechseln parallele Daten (8- oder 16-Bit) in schnelle serielle Streams. Geschwindigkeiten erreichen 2,5 Gbps pro Spur mit 200 mV HS-Swing und 1,2 V LP-Signalisierung. Modeschalter passieren schnell. Dies hält den Strom in ruhigen Zeiten niedrig.

Für 60 fps Video auf einem Smartphone startet DSI den HS-Modus für Framebursts. Dann fällt es in den LP-Modus zwischen Bildern. Die Schnittstellenleistung fällt von über 50 mW auf unter 5 mW. PHY hält die Signalqualität über Spuren stark. Es zielt auf Bitfehlerraten unter 10^-12 ab. DSI fügt CRC-Fehlererkennung hinzu, um zu helfen.

Häufige PHY-Optionen für DSI umfassen diese.

-

D-PHY: Es führt seit über zehn Jahren. Es verwendet 1 Uhr 1-4 Datenspuren (maximal 9 Drähte). Es erweist sich als zuverlässig für die meisten mobilen und eingebetteten Displays.

-

C-PHY: Es wendet eine 3-Phasen-Codierung auf Trios an (3 Drähte pro Spur). Dadurch wird eine bessere Spektraleffizienz erzielt. Zwei Trios (6 Drähte) können 4-Spuren D-PHY Bandbreite schlagen. Es eignet sich für enge Räume mit hochauflösenden Panels wie 4K.

Die ausgewählte PHY legt Bandbreite, Stromverbrauch und Pin/PCB-Bedürfnisse fest. D-PHY deckt die meisten mobilen Displays ab. Fortgeschrittene wie C-PHY bewältigen die wachsenden Anforderungen an die Auflösung.

FAQ (häufig gestellte Fragen)

Was ist der Hauptvorteil von MIPI DSI gegenüber parallelen Schnittstellen?

MIPI DSI reduziert die Anzahl der Pins um über 80%. Es senkt den Stromverbrauch durch Modeschalten. Es unterstützt hohe Bandbreite für aktuelle Auflösungen. Es reduziert auch EMI.

Welche PHY wird am häufigsten mit MIPI DSI in mobilen Geräten verwendet?

D-PHY bleibt die am häufigsten verwendete. Es verdankt dies seiner langen Geschichte, einfacheren Konstruktion und großer Energieeffizienz für Display-Refresh-Muster.

Kann MIPI DSI 4K-Displays bei 60 Hz unterstützen?

- Ja. - Ja. Ein 4-Spuren-D-PHY-Setup mit 2,5 Gbps pro Spur bietet ausreichende Bandbreite (insgesamt fast 10 Gbps). Es verarbeitet 4K bei 60 Hz, einschließlich Overhead.

Was ist der Unterschied zwischen dem Videomodus und dem Befehlsmodus in DSI?

Der Videomodus streamt Pixeldaten ohne Stopps. Der Befehlsmodus sendet komprimierte Bilder und Anweisungen an einen On-Panel-Puffer. Das Panel erfrischt sich selbst. Dies ermöglicht eine bessere Energieeinsparung für stille Inhalte.

Ist M-PHY mit MIPI DSI kompatibel?

M-PHY funktioniert hauptsächlich mit anderen Protokollen wie UniPro. DSI paart sich normalerweise mit D-PHY oder C-PHY. Neuere Bemühungen betrachten M-PHY für erweiterte Anzeigeaufgaben.

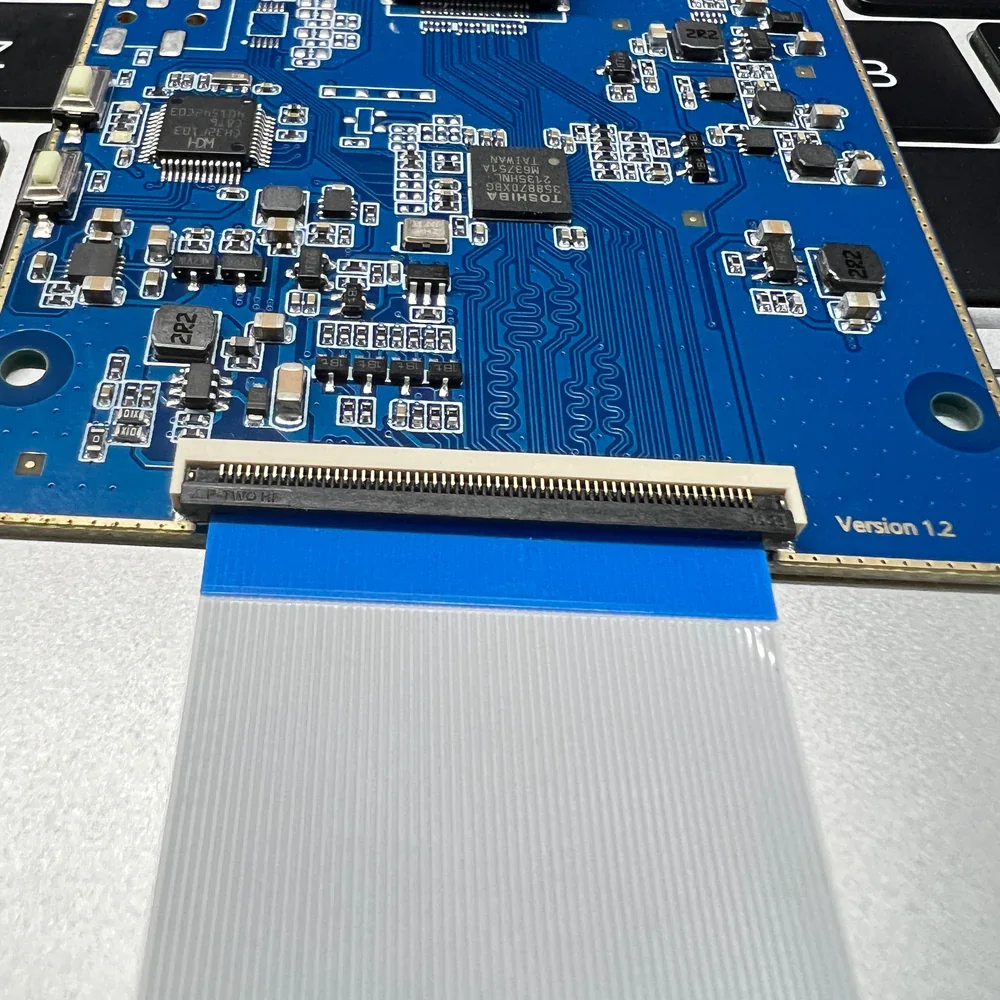

Partner mit einem vertrauenswürdigen Displayhersteller

Kadi Anzeige steht als professioneller Hersteller, Lieferant und Fabrik, die sich auf hochwertige TFT-LCD-, OLED-, AMOLED- und kundenspezifische Anzeigelösungen spezialisiert hat. Mit über 20 Jahren Erfahrung, einer Produktionsanlage von 10.000 Quadratmetern in Shenzhen, China und Zertifizierungen wie ISO9001, ISO14001, ISO13485 und IATF16949 liefert das Unternehmen zuverlässige industrielle, medizinische und eingebettete Displays. Produkte unterstützen Schnittstellen wie MIPI DSI, HDMI und mehr mit Anpassungsmöglichkeiten für verschiedene Anwendungen.

Hersteller, OEMs und Lieferanten, die maßgeschneiderte Anzeigemodule, wettbewerbsfähige Preise, schnelle Prototypierung oder Massenproduktion suchen, profitieren von Kadi Display’ s One-Stop-Service, strenge AOI-Qualitätskontrolle und engagierte technische Unterstützung.

Kontaktieren Sie das Team noch heute bei Sales@sz-kadi.com oder 86-13662585086, um Projektanforderungen zu diskutieren, Muster anzufordern oder kundenspezifische MIPI DSI-integrierte Lösungen zu erkunden. Steigern Sie die Produktleistung mit bewährter Display-Expertise.

Neueste Blog & Nachrichten

- IPS vs. andere Panels Wie man Displayschnittstellen für eingebettete und industrielle TFT-LCD auswählt

- 7-Zoll-MIPI-DSI-Displays: Top-Spezifikationen und beste Auswahl im Jahr 2026

- Wide Temperatur TFT Displays für industrielle Anwendungen

- Wie AG, AF und AR Lösungen kritische Anzeigeprobleme lösen

- Ein Schritt-für-Schritt-Leitfaden zum Mastering von MIPI DSI