MIPI Display Interface in Industrial LCD Systems

A Working Engineer’s Guide to DSI, PHY Selection, PCB Layout, and Real-World HMI Deployment

By Kadi Display Technical Team | www.kadidisplay.com

From Smartphones to Factory Floors: The Unexpected Journey of MIPI

Here’s something that doesn’t come up often in datasheet reviews: the interface running inside the display on your industrial PLC panel almost certainly started its design life as a spec for a Nokia or Samsung handset. That’s not a criticism — it’s actually why it works so well.

The MIPI Alliance was set up in 2003. The founding members — Arm, Nokia, STMicroelectronics, Texas Instruments — had a specific and practical goal: stop every phone manufacturer from rolling their own internal bus for connecting processors to camera sensors and displays. The fragmentation was costing everyone money. By 2005, the first Display Serial Interface spec was out. By 2010, it was in nearly every smartphone shipped. By 2015, industrial designers started paying serious attention.

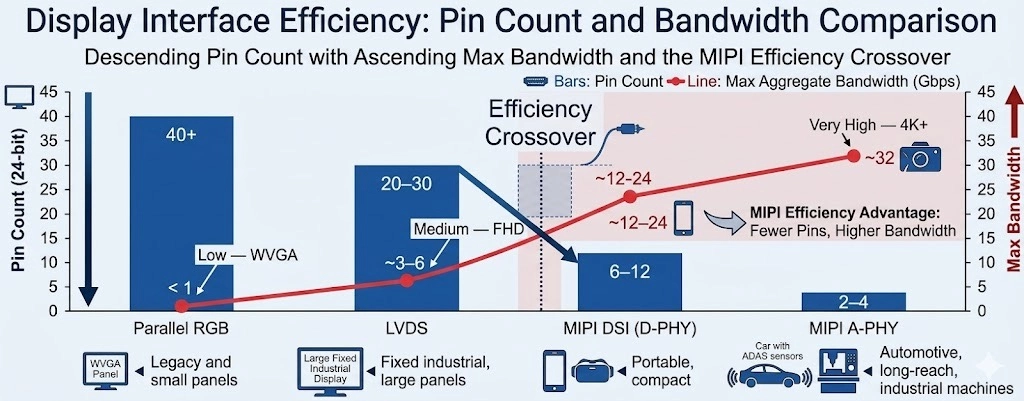

What made the crossover happen? A few things converged. Factory HMI requirements started demanding resolutions that parallel RGB simply couldn’t feed fast enough without turning PCBs into rats’ nests of 40-pin connectors. Medical imaging equipment needed tighter EMI control. Automotive cockpit designers wanted to push displays further from the SoC — sometimes across an entire door panel. MIPI’s underlying physics turned out to be exactly what all three sectors needed, even though it was never designed with them in mind.

This guide walks through how the MIPI display interface actually works — the PHY layer choices, what they mean in a real PCB layout, how driver IC bring-up tends to go wrong, and what to think about before specifying it for your next industrial or medical product. We’ll also cover where legacy LVDS still makes sense, because the honest answer is: it sometimes does.

If you’re starting from scratch on display interface selection, Kadi Display’s overview at Escolhar o melhor visor para seu dispositivo incorporado covers the broader decision tree before you get into MIPI specifics.

The Basics: What MIPI DSI Is Actually Doing

MIPI DSI — Display Serial Interface — is a point-to-point serial link. One transmitter (your SoC), one receiver (your display driver IC). That’s it. No bus arbitration, no shared medium. Data flows in one direction for pixel content, with a low-speed return path for command acknowledgment and touch data on some configurations.

The link is built from lanes. Each lane is a differential pair: two conductors, signals opposite in polarity, noise cancellation built into the physics. One of those lanes is a dedicated clock. The rest carry data. Most industrial panels you’ll encounter run on two or four data lanes; single-lane configurations exist but top out at around 1080×1920 at 60 Hz, and you’ll hit that ceiling faster than you expect if you add any compression.

Two modes govern how the SoC talks to the panel. Video mode is the simpler one: the host continuously streams pixel data, frame after frame, like an old CRT raster scan. The panel has no memory of its own — it just displays whatever it receives. Most high-refresh-rate industrial displays run this way. Command mode is different: the panel has an onboard frame buffer. The SoC sends updates only when something actually changes on screen, then lets the panel self-refresh. For a dashboard that mostly shows static process values with occasional alerts, command mode can cut interface power substantially — sometimes by half or more.

For a deeper look at the packet-level protocol — how short and long packets are framed, what the interface state machine looks like — Kadi’s technical breakdown is worth reading: MIPI Display Serial Interface (DSI) — Protocol Detail.

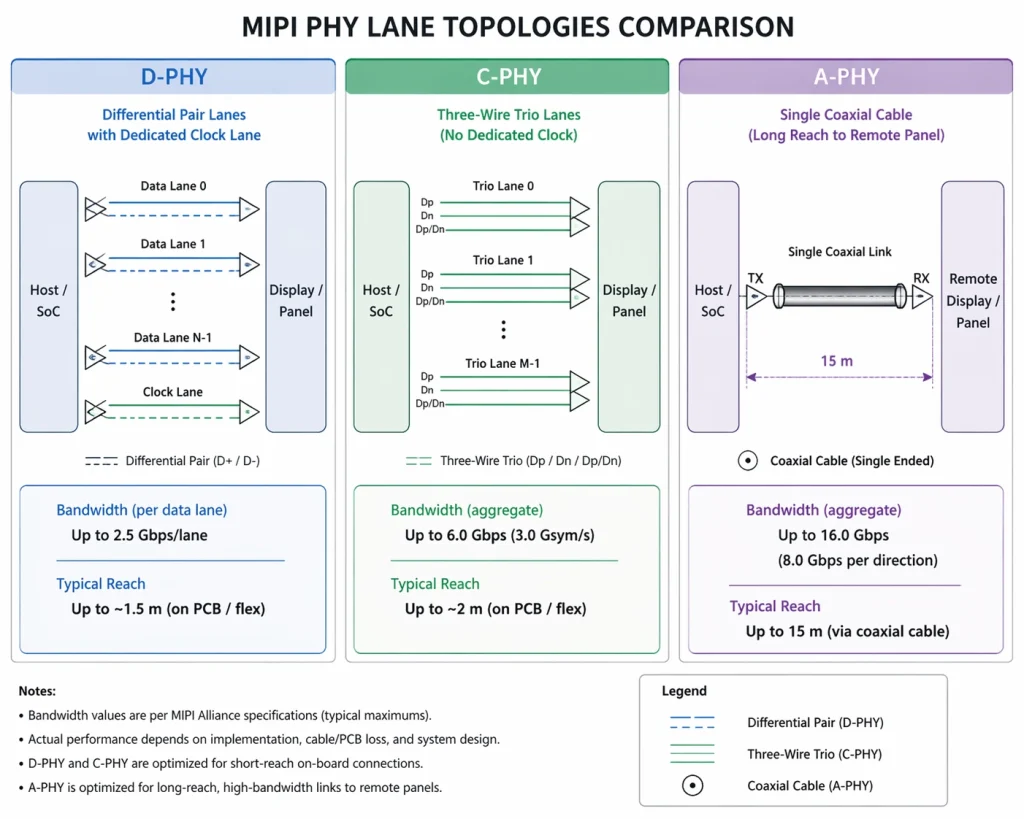

Choosing a Physical Layer: D-PHY, C-PHY, and A-PHY

This is where engineers tend to get confused, because “MIPI” and “D-PHY” get used interchangeably in most product briefs — but they’re not the same thing. D-PHY is the most common physical layer, yes. But it’s not the only option, and the differences between the three available PHYs matter quite a bit depending on what you’re building.

D-PHY: The one you’ll use 90% of the time

D-PHY uses standard differential signaling with a dedicated clock lane. The voltage swing is low — around 200 mV — which is part of why it radiates less than LVDS. Data rates have climbed over successive spec revisions: v1.2 topped out at 2.5 Gbps per lane (10 Gbps aggregate on four lanes), v2.1 pushed that to 6.5 Gbps per lane, and v3.5 introduced an embedded clock mode that freed up the clock lane for data.

For most 7-inch to 10.1-inch industrial panels running 1280×800 or 1920×1200 at 60 Hz, D-PHY v1.2 is still perfectly adequate. You don’t need v2.1 unless you’re pushing 4K or running at high frame rates. Picking the newest spec when older silicon supports v1.2 natively just adds bring-up complexity for no gain.

The power management behavior matters in practice. D-PHY switches between High-Speed mode (HS, for pixel data) and Low-Power mode (LP, for control signaling and lane idle). Each transition takes a few hundred nanoseconds. For continuous video this is invisible; for command-mode displays sending frequent small updates it can add up, and some driver ICs handle the LP-to-HS transition more gracefully than others. Worth checking in your panel’s datasheet before assuming command mode will work the way you expect.

C-PHY: When EMI is the constraint

C-PHY is the option nobody talks about until they’re sitting in an EMC pre-compliance test watching a Class 5 CISPR 25 failure they can’t explain. Instead of wire pairs, C-PHY uses wire trios — three conductors per lane, three-phase symbol encoding. Each symbol transition carries roughly 2.28 bits, so you get more data per clock edge. The side effect is that the spectral energy is spread more evenly across frequencies rather than concentrating at the fundamental clock rate. That’s what helps with EMI.

C-PHY v2.0 can push 44.5 Gbps aggregate, which is enough for uncompressed 8K. In practice, the industrial use case for C-PHY is primarily medical imaging — CT gantry displays, ultrasound consoles, surgical visualization systems where the display is mounted centimeters from high-frequency RF equipment and the regulatory bill of materials doesn’t allow much shielding mass. If you’re not in that situation, D-PHY is simpler to implement.

A-PHY: Solving the cable-length problem

Both D-PHY and C-PHY are limited to roughly one meter of cable reach. That’s fine for a tablet or a handheld terminal. It’s not fine for a large CNC center where the display panel is bolted to the operator station 3 meters away from the control cabinet, or a truck dashboard where the main display is 2 meters from the domain controller. Those deployments historically required proprietary SerDes bridge chips — extra cost, extra latency, extra bill-of-materials line items.

A-PHY eliminates the need for those bridges. It’s a long-reach serializer/deserializer specified at up to 15 meters, running at up to 32 Gbps downlink (v2.0) over standard coaxial or shielded twisted-pair cable. The uplink path — for touch, haptic feedback, camera metadata — runs at up to 1.6 Gbps. The packet error rate specification is 10⁻¹⁹, which is unusually aggressive; it’s calibrated for safety-critical applications where a corrupted pixel in a warning display is a regulatory incident.

A-PHY is the physical foundation of the MIPI Automotive SerDes Solutions (MASS) framework, which layers ISO 26262 functional safety and HDCP content protection on top. If you’re designing instrument cluster displays or in-cabin HMI for vehicles, this is the architecture to understand. For embedded systems work more broadly, the MIPI DSI mastering guide covers how these PHY choices connect to real system design.

How MIPI DSI Compares to LVDS and Parallel RGB in Practice

Before going further into implementation, it’s worth being direct about where each interface actually fits — because the marketing materials for MIPI tend to make LVDS sound obsolete, and that’s not entirely accurate.

Parallel RGB is genuinely obsolete for anything above WVGA resolution. The pin counts are unmanageable, the skew requirements at high frequencies demand PCB layers you’d rather not spend, and the power draw is constant regardless of content. If you’re inheriting a design that uses it, budget for a redesign. If you’re starting fresh and you’re somehow considering it: don’t.

LVDS is a different story. For displays in the 10-inch to 21-inch range — industrial monitors, medical imaging panels, point-of-sale terminals — LVDS is still a rational choice, particularly if your SoC or FPGA has mature LVDS output support and you don’t need the bandwidth for 4K. The 10-meter cable reach is genuinely useful, the ecosystem is deep, and the bring-up process is well understood. The power and PCB-space disadvantages are real, but they don’t automatically make LVDS the wrong answer for fixed industrial equipment where neither is a hard constraint.

Where MIPI DSI clearly wins: portable equipment, battery-powered devices, any application where PCB size matters, anything running 4K resolution, and any product line where you want to leverage the same display SoC IP across both a consumer and industrial variant.

PCB Layout: Where MIPI Implementations Actually Break

If you talk to engineers who’ve brought up MIPI DSI hardware, the conversation about what went wrong almost always comes back to the PCB. The protocol is straightforward enough. The driver IC bring-up is manageable. The layout is where the gotchas live — and there are more of them than the spec documents tend to emphasize.

Impedance control is non-negotiable

At 2.5 Gbps per lane, your differential traces are transmission lines. They behave like transmission lines. Ignore that fact and you’ll get reflections — which manifest as pixel errors, jitter, and intermittent lock failures that are maddening to debug because they’re often temperature- and load-dependent. The target is 100 Ω differential impedance, ±10%. That’s tighter than it sounds given typical PCB manufacturing tolerances, and it means you need to specify stackup and trace geometry explicitly with your board house, not leave it as an assumption.

One thing that catches designers: the differential impedance calculation changes when you route over gaps in the ground plane. It also changes when you pass near a power island. Plan your layer stackup before you route the MIPI lanes, not after.

Length matching and what it actually means

The lanes need to match in length — the common instruction is “within 5 mils.” That’s true, but the less-stated requirement is that the two traces within each differential pair also need to match. Intra-pair skew is often worse than inter-lane skew in practice, because designers obsess over keeping the clock lane the same length as the data lanes but let the P and N traces of a single pair drift apart through a curve or a via transition. The symptom is a subtly corrupted display that works perfectly on the bench but fails at operating temperature or under vibration.

Vias, connectors, and the ground plane

Every via in your MIPI traces is an impedance discontinuity. Minimize them. When you can’t avoid a via transition — layer change for a connector, say — add ground-stitching vias around each signal via. The return current needs a low-impedance path, and without the stitching vias it’ll find one elsewhere, creating a loop antenna.

FPC connectors are another common failure point. The contact interface at the connector typically breaks the controlled-impedance geometry. Some connector families handle this better than others. Check insertion loss specifications for your connector at the actual signaling frequency, not just at DC.

Driver IC Bring-Up: What the Datasheets Don’t Tell You

MIPI DSI is not plug-and-play. That sounds obvious when you say it, but it genuinely surprises engineers coming from HDMI or DisplayPort backgrounds. There’s no hot-plug detect, no EDID negotiation, no automatic mode discovery. The host SoC needs to know — precisely — the timing parameters your specific panel requires, and it needs to send the driver IC’s initialization command sequence in the correct order before sending pixel data. Get either of those wrong and you get nothing: a blank panel, an intermittent display, or (rarely) a panel that powers on but renders incorrectly.

The three driver ICs that appear most often in 5-inch to 10-inch industrial panels are the ILI9881C (common on 720p portrait-orientation panels), the EK79007 (standard for 1024×600 and 1280×800 landscape modules), and the ST7701S (widespread in square-format and small industrial displays). All three are well-documented, and all three have quirks in their initialization sequences that aren’t well-documented.

A few things worth knowing from bring-up experience:

- The panel reset signal timing is almost always tighter than the datasheet implies. If your display flickers during power-on but works fine once it’s running, check whether your reset pulse duration and the delay before your first DSI command are both meeting the minimum specs — and then add margin.

- The Linux DRM/KMS driver framework is the right path for any SoC running mainline Linux. Writing a framebuffer driver from scratch is unnecessary and creates long-term maintenance burden. The panel driver (for the driver IC) and the DSI host driver (for the SoC’s controller) are separate modules. Many industrial SoCs — NXP i.MX 8 series, Rockchip RK3566, Allwinner H6 — have upstream DSI host drivers. Your work is usually the panel driver, which means getting the init sequence and timing parameters right.

- If you’re using a Raspberry Pi-based platform, MIPI DSI bring-up has its own specific device tree overlay workflow. Kadi Display’s step-by-step DSI connection guide for Raspberry Pi covers this in practical detail, including the overlay syntax and common configuration mistakes.

- Timing parameters — hsync/vsync front porch, back porch, pulse width — must be matched precisely to the panel driver IC’s requirements. These values come from the panel manufacturer. If you’re using a Kadi Display module, they’re in the product datasheet. If you’re sourcing panels independently, treat the manufacturer’s timing spec as a hard constraint, not a suggestion.

For a comprehensive technical walkthrough of DSI at the protocol level — state machine, packet types, lane management — the MIPI DSI interface overview is a useful reference before diving into bring-up.

Environmental Requirements for Industrial Deployments

Consumer electronics live in climate-controlled rooms. Industrial electronics do not. A MIPI display module that works fine in a lab at 25°C needs to keep working in a cold storage facility at −20°C, on the side of a packaging machine where the enclosure heats to 60°C, in a marine navigation terminal with high humidity cycling, and — for automotive applications — across the full −40°C to +85°C extended-temperature range.

The interface itself doesn’t have temperature-dependent behavior that causes problems — D-PHY timing parameters are specified with sufficient margin for industrial temperature ranges. The constraints come from the LCD panel, the driver IC, and the backlight assembly. Industrial-grade panels use LC mixtures with lower viscosity change across temperature, preventing the sluggish response or optical artifacts that consumer panels show below 0°C. The backlight needs to be specified for the thermal environment too — LED efficiency drops with temperature, and a backlight sized for 1,000 nits at 25°C may fall short at −20°C if the driver isn’t compensating.

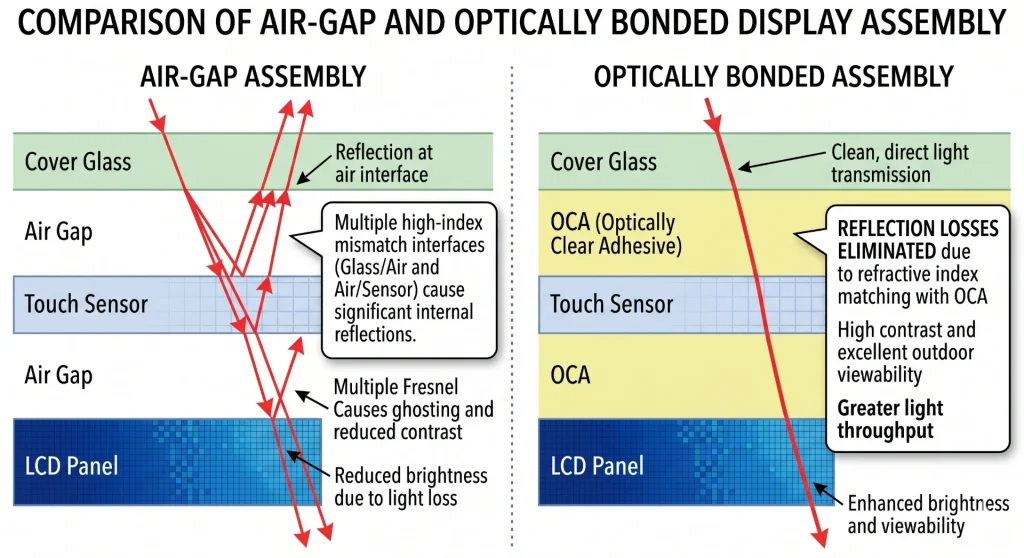

Optical bonding and why it matters in real deployments

Optical bonding — bonding the cover glass directly to the LCD panel face using OCA film or OCR resin, eliminating the air gap — isn’t just a nice-to-have for sunlight readability. In temperature-cycling environments, an air-gap assembly creates condensation problems: moisture migrates into the gap and fogs the display from the inside. In vibration environments, the gap allows mechanical movement between the glass and the panel that eventually causes delamination or touch calibration drift.

The readability improvement from optical bonding in high-ambient-light conditions is measurable — studies in the field consistently show 30–40% contrast improvement under direct sunlight compared to air-gap assemblies — but the durability argument is often what actually drives the decision for industrial customers. The full technical breakdown of bonding process options (wet OCR, dry OCA/SOCA) is covered in Kadi Display’s guide: Optical Bonding — How to Combine Display with a Touch Panel.

For the wider topic of wide-temperature display selection, including LC mixture choices and backlight thermal management considerations, see: Wide Temperature TFT Displays for Industrial Applications.

Where MIPI Fits in Industrial Application Segments

Factory automation and process HMI

The bulk of industrial MIPI deployments are HMI panels: the operator interface screens on CNC machines, process controllers, and assembly line stations. Panel sizes in this segment run mostly 7 to 10.1 inches. Resolution requirements are 800×480 on the low end, 1280×800 increasingly common, with 1920×1200 appearing on high-end visualization nodes. Brightness specs for industrial environments typically start at 800 nits and go up — ceiling-mounted fluorescent lighting in a factory is surprisingly bright, and reflections off a low-brightness panel in a stainless-steel environment are a real usability problem.

The full range of HMI display considerations — response time, touch technology, viewing angle requirements, MTBF specifications — is covered in detail in: How Open Frame Touchscreen Monitors Are Used for Industrial HMI Automation. For background on what HMI systems actually do in a plant context: What is HMI Screen? Common Uses, Trends and the Future of HMI.

Medical devices

Medical display requirements stack multiple constraints simultaneously: IEC 60601-1 electrical safety, EMC compliance in environments packed with RF equipment, chemical resistance for disinfection protocols, and — for diagnostic applications — color accuracy standards that exceed typical industrial requirements. MIPI DSI with C-PHY suits medical applications particularly well because the EMI profile is lower than D-PHY at equivalent bandwidth, which eases CISPR compliance in RF-dense environments. Optical bonding is essentially standard in portable medical equipment: the environmental sealing it provides against moisture and cleaning chemicals is as important as the optical improvement.

Automotive and in-vehicle displays

In-vehicle applications are where A-PHY earns its specification. The combination of ISO 26262 functional safety requirements, CISPR 25 EMC limits, extended temperature range, and the physical separation between domain controllers and display panels creates a requirement set that nothing before A-PHY adequately addressed without proprietary hardware. If you’re designing instrument cluster displays, center console touchscreens, or rear-seat entertainment systems, the MASS framework is worth understanding from the beginning of the architecture phase, not as an afterthought.

Display Stream Compression and Future Directions

As panel resolutions increase, raw bandwidth requirements start to exceed what even high-lane-count D-PHY can deliver without going to C-PHY. A 4K panel at 60 Hz in 24-bit color needs roughly 14.9 Gbps of raw pixel data. That’s four lanes of D-PHY v2.1 running at near-maximum rate, with no headroom for overhead. Display Stream Compression (DSC), incorporated into the MIPI DSI-2 specification alongside the VESA DSC standard, addresses this by reducing the data volume 3–6× while maintaining visually lossless image quality.

DSC allows 4K content to run on two D-PHY lanes instead of four — which has direct downstream effects on PCB complexity, connector size, and power consumption. The compression is mathematically lossless in terms of visual perception; independent evaluations consistently find that DSC-compressed and uncompressed streams are indistinguishable to the human eye under normal viewing conditions.

Beyond DSC, two trends are worth watching for industrial applications. First, the shift toward zonal architectures in both automotive and high-end industrial systems — where a single domain controller manages multiple camera and display streams over a common high-bandwidth backbone — creates exactly the deployment scenario A-PHY was designed for. Second, MIPI Touch is in active development: a specification to carry touch data on the same serial link as display data, eliminating the separate I²C or SPI touch controller wiring that currently adds complexity to every capacitive touch HMI.

Perguntas Frequentemente Fazidas

Q: Is MIPI DSI harder to implement than LVDS?

Honestly, yes — initially. LVDS has a simpler bring-up process and more forgiving PCB layout tolerances. MIPI DSI requires tighter impedance control, precise driver IC initialization sequences, and (on Linux) correct device tree configuration. The payoff is lower power, higher bandwidth, and a smaller PCB footprint. For teams with no prior MIPI experience, budget for a longer bring-up cycle on the first design.

Q: Can I use A-PHY for an industrial machine where the display is 5 meters from the controller?

Yes, and it’s probably the right call. A-PHY is specified to 15 meters and eliminates the proprietary SerDes bridge chips that the same application would have required with D-PHY. The functional safety features in the MASS framework are optional if you don’t need ISO 26262 compliance — you can implement A-PHY purely for the reach and bandwidth benefits.

Q: What panel driver ICs are most common in industrial MIPI modules?

For 5–7 inch panels, ILI9881C (720p portrait) and ST7701S (small/square format) are the most common. For 7–10.1 inch landscape panels at 1024×600 to 1280×800, EK79007 dominates. All three have mature Linux driver support. Initialization sequences vary between batches from some suppliers — if you’re sourcing modules in quantity, request the initialization register dump for your specific batch.

Q: Does optical bonding affect MIPI interface performance?

No direct effect on the interface. Optical bonding is a display assembly technique that affects optical performance, mechanical durability, and environmental sealing. It doesn’t change anything about how the MIPI lanes operate. That said, the combination of a high-brightness MIPI panel with optical bonding is essentially standard for outdoor-facing or high-ambient-light industrial installations — the interface and the assembly method are complementary parts of the same design decision. More details at: O que é a ligação óptica? Um Guía para Mostras Industriais.

Q: Is MIPI DSI supported on Raspberry Pi?

Yes — all Raspberry Pi models from Pi 1 through Pi 5 include a DSI connector. The Pi 5 improved the DSI host controller significantly. Bring-up requires device tree overlay configuration rather than plug-and-play detection. Kadi Display’s Raspberry Pi MIPI DSI connection guide covers the full process, including the specific overlay syntax and common failure modes.

Conclusão

The MIPI display interface didn’t become the standard for industrial LCD systems because someone decided it should. It got there because the physics worked out: low voltage swing, serialized data, differential noise rejection, and a PHY roadmap that kept pace with resolution and bandwidth requirements. The fact that the mobile industry had already solved the manufacturing scale problem — driver ICs, SoC IP blocks, connector families — made it easy to adopt in sectors where those supply chains didn’t exist before.

The practical reality of working with MIPI DSI is that the protocol itself is manageable, but the implementation details — PCB layout discipline, driver IC bring-up, device tree configuration — require care. Engineers who treat it as a plug-and-play interface the first time generally have a bad experience. Engineers who approach it as a transmission-line problem with a software bring-up component get it working reliably.

For product designs where power budget, PCB space, and resolution requirements make MIPI the logical choice — and that covers most new industrial HMI, medical device, and automotive display designs — it’s worth investing in the implementation rigor upfront. The gains are real and sustainable across the product lifecycle.

Kadi Display’s full range of industrial MIPI LCD modules — including high-brightness IPS panels, optically bonded configurations, wide-temperature variants, and custom PCBA integration — is available at: www.kadidisplay.com. For specification queries or custom development enquiries, the technical team can be reached directly through the site.

Further Reading — Kadi Display Technical Resources

- What Is MIPI DSI? Advantages and Technical Overview

- MIPI Display Serial Interface (DSI) — Protocol Reference

- Um guia passo por passo para masterizar a MIPI DSI

- Como conectar um display LCD de DSI MIPI a um Raspberry Pi

- What Is the MIPI DSI Port on Raspberry Pi?

- Optical Bonding — How to Combine Display with a Touch Panel

- O que é a ligação óptica? Um Guía para Mostras Industriais

- Como os monitores de ecrã de toque aberto são usados para a Automatização Industrial da HMI

- Temperatura larga TFT mostra para aplicações industriais

- What is HMI Screen? Common Uses, Trends and the Future of HMI

- 7-Inch MIPI DSI Displays: Top Specifications in 2026

- Escolhar o melhor visor para seu dispositivo incorporado

Recent Blog & News

- MIPI Display Interface in Industrial LCD Systems

- LCD Screen Retention vs. Burn-in: Industrial Solutions and Prevention Guide (2026 Edition)

- Capacitive vs Resistive Touch Screen: Which Wins for Medical & Industrial?

- Sunlight Readable TFT LCDs: Essential for Outdoor Vehicles & Agricultural

- Best Industrial Touch Screen Displays for Harsh Environments